Cadence Design Systems (Nasdaq: CDNS) has announced a major advancement in memory technology with the launch of the industry’s first DDR5 12.8Gbps MRDIMM Gen2 memory IP system solution. Built on the TSMC N3 process node, the new offering is designed to meet the growing need for high bandwidth memory in artificial intelligence (AI), high-performance computing (HPC), and data center applications.

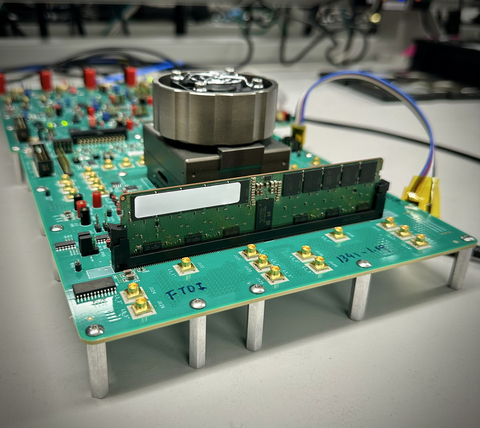

The memory subsystem solution, based on Cadence’s proven DDR5 and GDDR6 architectures, includes a complete PHY and high-performance controller validated with Gen2 MRDIMMs. The solution achieves 12.8Gbps data rates—double that of current DDR5 6400Mbps DRAM—providing a significant performance leap for systems requiring fast and scalable memory.

Cadence highlights that its DDR5 MRDIMM IP integrates features such as ultra-low latency encryption, high reliability, availability, and serviceability (RAS), and flexible power/performance tuning. It is tailored for advanced SoCs and chiplet architectures, making it an ideal choice for AI-driven cloud infrastructure.

Industry partners have expressed strong support. “Cadence’s DDR5 MRDIMM IP, alongside Montage’s memory buffers, delivers a high-performance memory subsystem for next-gen servers,” said Stephen Tai, president of Montage Technology. Montage’s MRCD02 and MDB02 chips are optimized for the new modules, supporting speeds up to 12.8Gbps.

Micron also praised the collaboration. “Our 1γ DRAM combined with Cadence’s DDR5 IP will address key AI processing challenges, offering greater memory bandwidth and density,” said Praveen Vaidyanathan, Micron’s VP of data center products.

Cadence’s DDR5 solution has already seen early adoption among leading customers in the AI and data center space. With verification supported by Cadence’s DDR5 Verification IP (VIP), the company promises rapid SoC design closure and a robust roadmap for future scalability.