Ubiquitous compute, pervasive connectivity, artificial intelligence and cloud-to-edge infrastructure drive a diverse and expanding range of computing workloads from the desktop to the data center.

At Architecture Day 2021, Intel detailed the company’s architectural innovations to meet this exploding demand, setting the stage for new generations of leadership products. Intel architects provided details on two new x86 central processing unit architectures; Intel’s first performance hybrid architecture and Intel® Thread Director; Intel’s next-generation data center processors; infrastructure processing unit architectures; and upcoming graphics architectures.

x86 Architectures: With its Efficient-core and its Performance-core, Intel signals the biggest architectural shift in a generation for x86 central processing units. The Efficient-core microarchitecture is designed for throughput efficiency and efficient offloading of background tasks for multitasking. It runs at low voltage and creates headroom to increase frequency and ramp up performance for more demanding workloads. The Performance-core microarchitecture is designed for speed, the highest performing CPU core Intel has built. It pushes the limits of low latency and single-threaded application performance and provides a significant boost at high-power efficiency that can better support large applications.

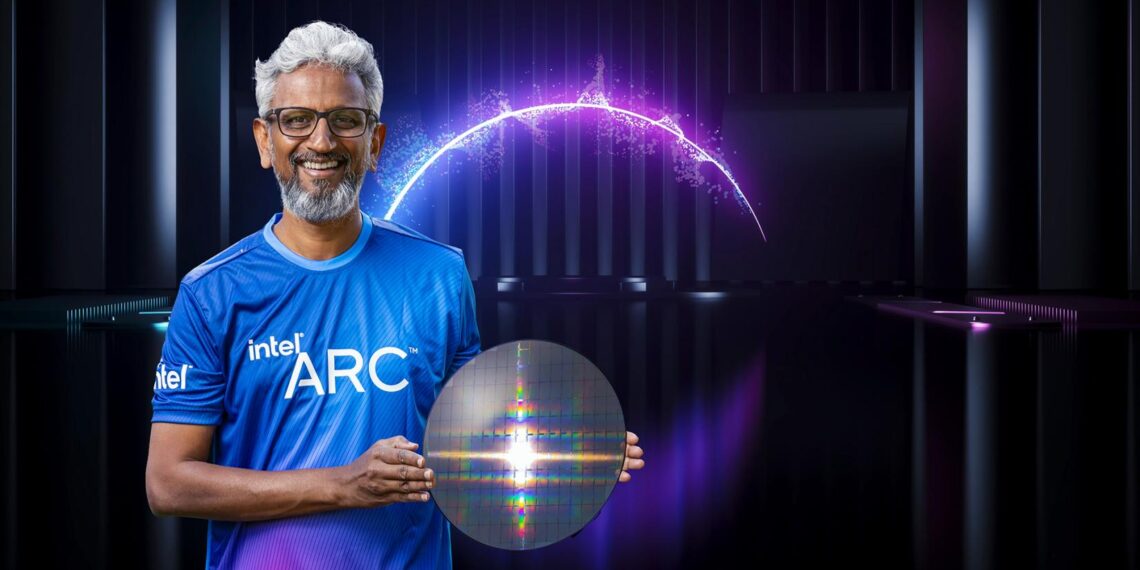

Client Computing – Graphics: Xe-HPG is a new discrete graphics microarchitecture for gamers and creators designed for scalability and enthusiast-class performance with a software-first approach. Products based on this microarchitecture will come to market in the first quarter of 2022 under the Intel Arc brand and Alchemist family of system-on-chips.

Data Center – Sapphire Rapids: Combining Intel’s Performancecores with new accelerator cores, “Sapphire Rapids,” the next generation of Intel Xeon Scalable processors, represents the industry’s biggest data center platform advancement in over a decade. The processor delivers substantial compute performance across dynamic and increasingly demanding data center usages and is workload-optimized to deliver high performance on elastic compute models like cloud, microservices and artificial intelligence.

Data Center – Infrastructure Processing Unit: The IPU is designed to enable cloud and communication service providers to reduce overhead and free up performance for central processing units. Among the new IPU architectures: Mount Evans is Intel’s first ASIC IPU, designed to address the complexity of diverse and dispersed data centers. Oak Springs Canyon is an IPU reference platform built with the Intel Xeon D processor and the Intel Agilex FPGA. And the Intel N6000 Accelerated Development Platform is designed for use with Xeon-based servers.

Data Center – Ponte Vecchio: Based on the Xe-HPC microarchitecture, Ponte Vecchio delivers industry-leading FLOPs and compute density to accelerate artificial intelligence, high performance computing and advanced analytics workloads. Intel disclosed details of the Xe-HPC microarchitecture, including that A0 silicon performance is providing greater than 45 TFLOPS FP32 throughput, greater than 5 TBps memory fabric bandwidth and greater than 2 TBps connectivity bandwidth.